-

Notifications

You must be signed in to change notification settings - Fork 23

Home

The PiTubeDirect project is about implementing a range of historical Co Processors for the BBC Model B and BBC Master computers at the lowest possible cost using a Raspberry Pi.

The lowest cost solution comprises:

- a 40 pin IDC cable

- a pair of 74LVC245A's which shift the tube interface from 5V to 3.3V levels

- a Raspberry Pi Zero

- a micro SD card

- a Pi-compatible serial cable (optional, for debugging)

The Bill-of-Material for this is approximately ten pounds.

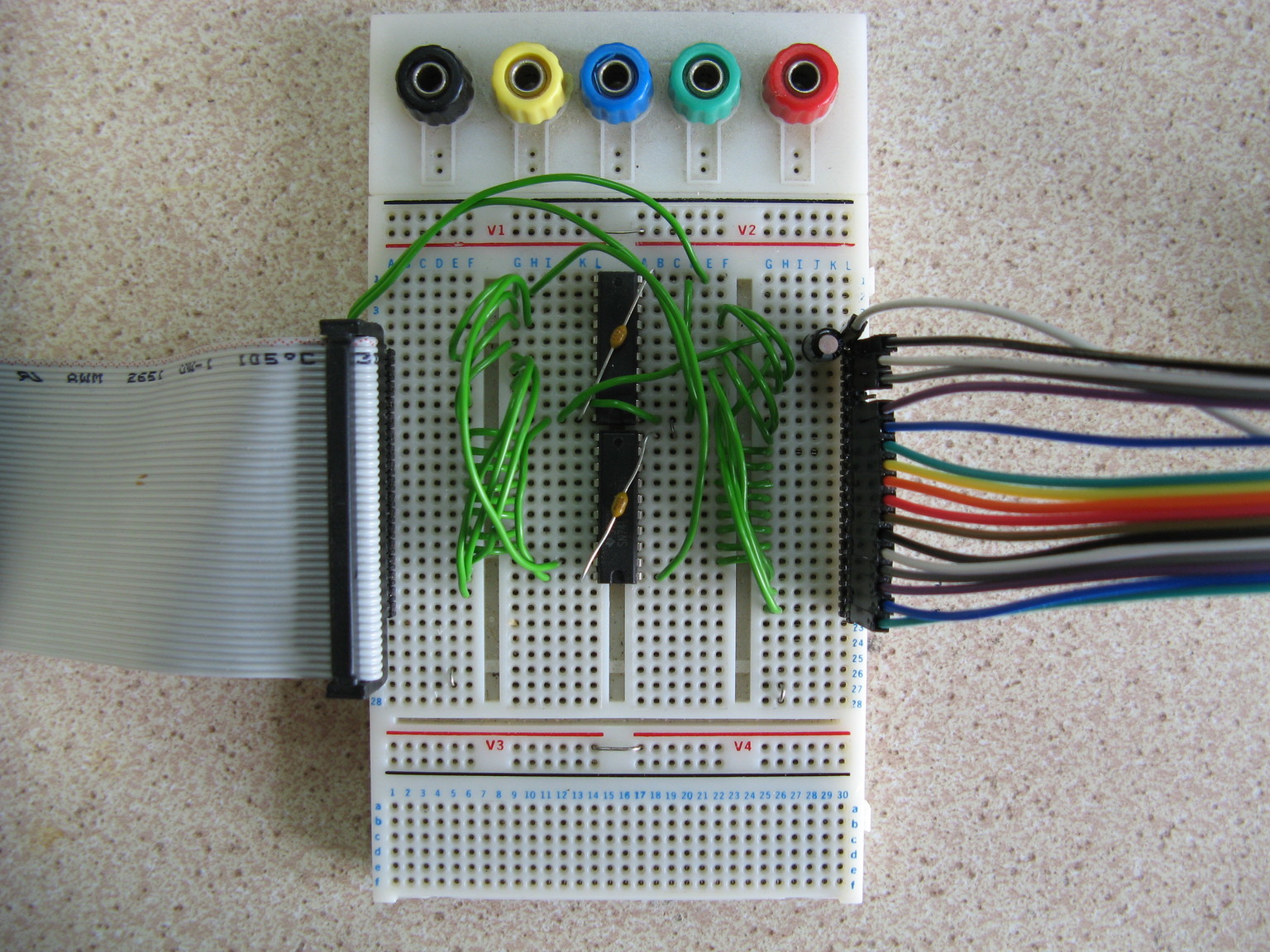

The minimal setup, using a Pi Zero and a DIY two-chip level shifter:

A closer view of the level shifter:

A closer view of the level shifter:

A closer view of the Pi Zero:

A closer view of the Pi Zero:

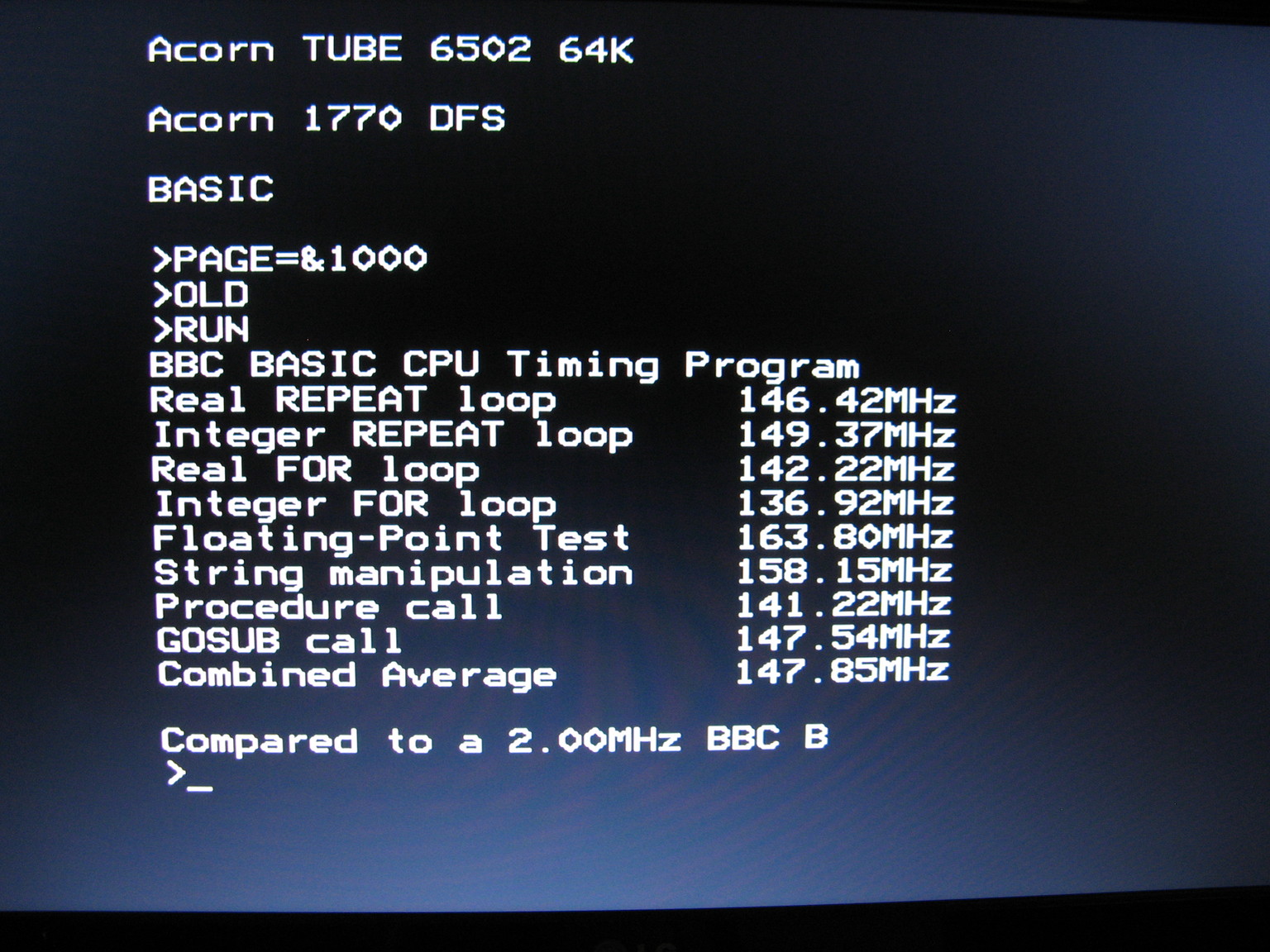

The 65C02 Co Processor running the CLOCKSP benchmark:

The 65C02 Co Processor running the CLOCKSP benchmark:

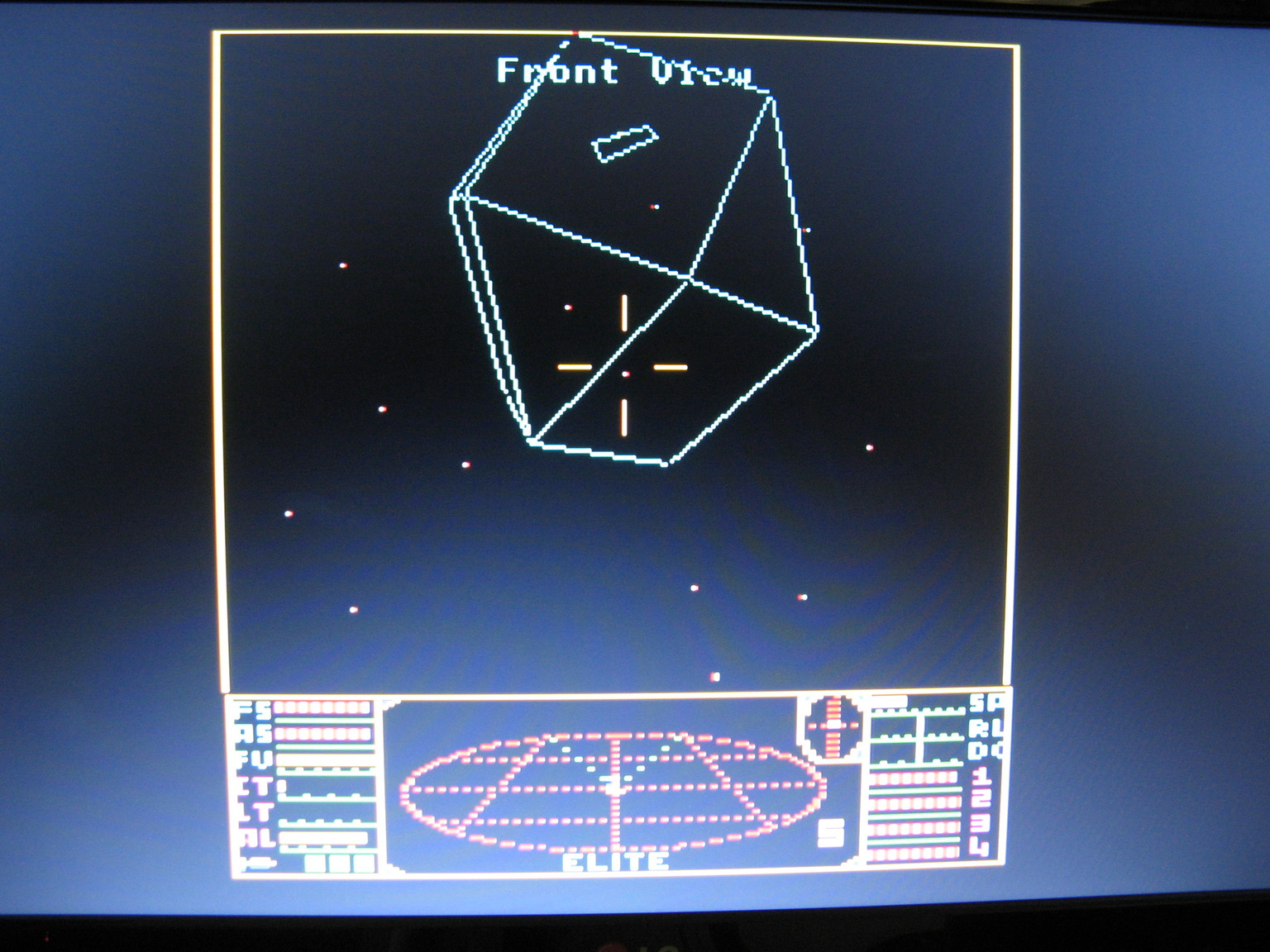

The 65C02 Co Processor running the Tube Elite:

The 65C02 Co Processor running the Tube Elite:

The ARM Co Processor running the CLOCKSP benchmark:

The ARM Co Processor running the CLOCKSP benchmark:

It's possible to dynamically switch between Co Processors using *FX 151,230,N (same mechanism the Matchbox Co Processor uses if you are familiar with that).

The Tube chip in an original BBC Co Processor is a custom ULA (Uncommitted Logic Array) that provides four bidirectional FIFOs, allows the BBC Micro (host) and the Co Processor (parasite) to reliably communicate by passing messages with full flow control.

In PiTubeDirect, the functionality of the Tube chip is emulated in software on the Raspberry Pi, and the Tube host interface on the BBC micro is connected to the Raspberry Pi's GPIO header via a pair of 74LVC245A level shifter chips.

The level shifters are necessary because the Tube interface uses 5V levels, where as the Raspberry Pi's GPIO signals uses 3.3V levels. Omitting the level shifters would likely damage the Raspberry Pi!

The Tube host interface is simply an extension of the 6502 bus and operates at 2MHz. The nTUBE signal (indicating an access to one of eight host-side tube registers) becomes active ~100ns into the 6502 bus signal. This generates an interrupt on the Pi, which then has about ~400ns (at most) to service the access in real time.

Clearly minimizing interrupt latency is crucial to reliable operation, and we use several techniques here:

- dispense with an operating system - PiTubeDirect is a bare metal firmware image

- use a FIQ interrupt (so registers don't have to be stacked)

- carefully hand optimize the FIQ handler

- avoid cache misses within the FIQ handler by locking critical code and data into the cache

- if multiple cores are available, dedicate an entire core to the FIQ handler

Doing all this, it's possible to achieve the required performance.

For more information, see the FIQ interrupt handler walkthrough

The PiTubeDirect firmware currently includes emulations of the following Beeb Co Processors:

- 65C102 (using 65tube - the fastest known native ARM 65C02 emulation)

- 65C102 (using lib6502 - written in C)

- 80x86 (using Fake86 - written in C)

- ARM2 (using MAME's ARM 2/3/6 emulation - written in C)

- 32016 (using a 32016 emulation that started life in B-Em, and was resurrected earlier this year)

There are plans to add a Z80 to this list.

See Credits and Acknowledgements for who we have to thank for each of these emulations, which all derive from the earlier PiTubeClientproject (more below).

Several Pi Models are supported, but within the team we are concentrating on the two extremes:

- the £4.00 Pi Zero (BCM2835/ARM1176) which has a single ARM core that runs at upto 1.0GHz

- the £30.00 Pi 3 (BCM2837/ARM Cortex A53) which has four ARM cores running at upto 1.2GHz

On the Pi Zero, the challenge is reducing interrupt latency, regardless of what the main emulator is doing, as they are both sharing on the same core. The typical interrupt latency we observe is 80ns. However, if the main emulator has a cache miss at exactly the same time as the host attempts to read a tube register, this can increase to 300ns, which means the read data arrives marginally late.

We have focused on the 6502 emulation using 65tube, which has been reduced in size to ~9KB. In theory this should fit inside the 16KB L1 cache. But in practice we observe occasional late reads (on the scope). That said, Tube Elite does run reasonably reliably. To be honest, we are close to the edge here, and this is best viewed as an experiment that's still in process.

On the Pi 3, we dedicate one of the cores to interrupt handling, and doing this results in an interrupt latecy that is very tightly controlled, and varies between 100ns and 120ns. This provides ample time to reliably service reads and writes, regardless how large the main emulator is, and what it is doing.

All of the emulators currently successfully boot on the Pi 3, and are more reliable than on the Pi Zero.

That said, I think there is still work to do!

PiTubeDirect is closely related, but distinct from, two earlier Beeb Co Processor projects:

- the Matchbox Co Processor (see github and stardot) implements multiple Co Processors using a Xilinx XC6SLX9 FPGA. More than 50 of these have been built and distributed through the stardot forums. The cost is about £50.

- the PiTubeClient project (see github and stardot is an extension to the Matchbox Co Processor that allows a range of Co Processors to be emulated in software on a Raspberry Pi. One of the designs in the Matchbox Co Processor is an "SPI Co Processor" containing an implementation of the Acorn Tube chip together with an SPI slave interface. A software emulation of a Co Processor, running on the Raspberry Pi, can use SPI to read/write the tube registers. The Raspberry Pi firmware to do all this is PiTubeClient.

PiTubeDirect is an evolution of PiTubeClient that avoids the need to use a Matchbox Co Processor. It does this emulating the Acorn Tube chip itself in software on the Raspberry Pi. This introduces some very hard real time constraints on the Raspberry Pi.

Hardware

Software

- Build dependencies

- Running cmake

- Compiling kernel.img

- Deploying on a Pi

- Recommended config.txt and cmdline.txt options

- Validation

- Compilation flags

Implementation Notes